IC設計先進分析與管理儀表板 Pinpoint

協助設計收斂的先進分析和管理儀表板 – ENOVIA Pinpoint

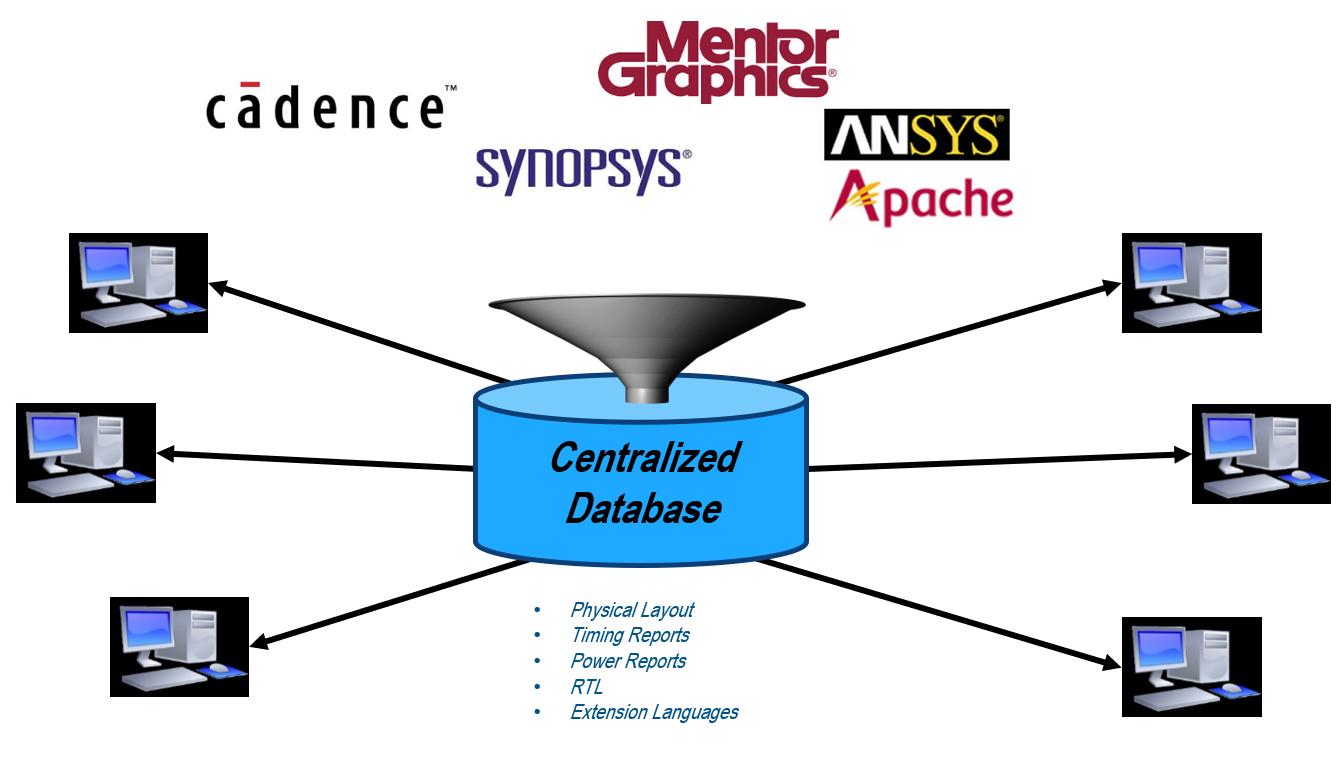

ENOVIA Pinpoint能夠自動爬梳IC開發流程中的各種前後段設計、模擬及驗證資料,並透過網站伺服器的使用,使半導體設計團隊能簡潔快速的以視覺化的方式檢視各種資料,加以跟蹤和預測設計的進程跟品質,大幅加強專案管控的能力,從而達到芯片準時tape-out的目的。ENOVIA Pinpoint交叉整理各類繁瑣的設計資料,以各種視覺及圖表方式呈現出問題所在,使設計團隊有效掌控及管理專案進度,便於快速解決問題,實現設計收斂。

芯片設計是一項挑戰嚴峻的工作,每天都有計畫進程被打亂的情形發生。計畫管理人員知道他們需要更快地評估問題所在,和設計團隊協力解決問題。但面對大量且龐雜的設計資料,以致不易抓住問題根本所在的情況下,設計完成時間超過預定的時程的事件屢見不鮮。

潛在的這些問題存在多重挑戰:

- 隨著IP模組被加入芯片佈局規劃中,設計收斂的複雜程度呈幾何級數成長。

- 設計收斂需要在達成功能性的同時,滿足時序、低功耗、面積、可製造性、高性能和消除熱點 (hot spot) 之間相互衝突的需求。

- 需使用不同工具驗證對不同規格的合規性。每種工具都會生成不同的資料格式,在沒有綜合性試算表的情況下,難以使用一個分析圖或分析圖表開展比較性分析。

由於為解決不同的工程問題,如邏輯簡化 (logic minimization)、時脈樹 (clock tree)、低功耗、佈局 (layout) 等等所使用的EDA工具不同,加上為達成設計收斂,在各種工程問題上都要求設計及驗證的反覆運算,這就對設計完成時間造成不利影響。

導致這些問題和痛點的原因:

- 導致延遲和低產品質量的主要原因是設計項目本身的複雜度、低效率的設計資料管理、以及受限於各種設計和驗證工具所產生的資料之間難以綜合分析。

- 工程團隊人員之間的溝通不良,導致設計不能按時的完成高品質成品。溝通可能受地理位置、時區、語言、文化、技能集和流程知識的制約。

- 設計及驗證所需的EDA工具購置預算有限。

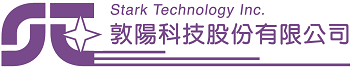

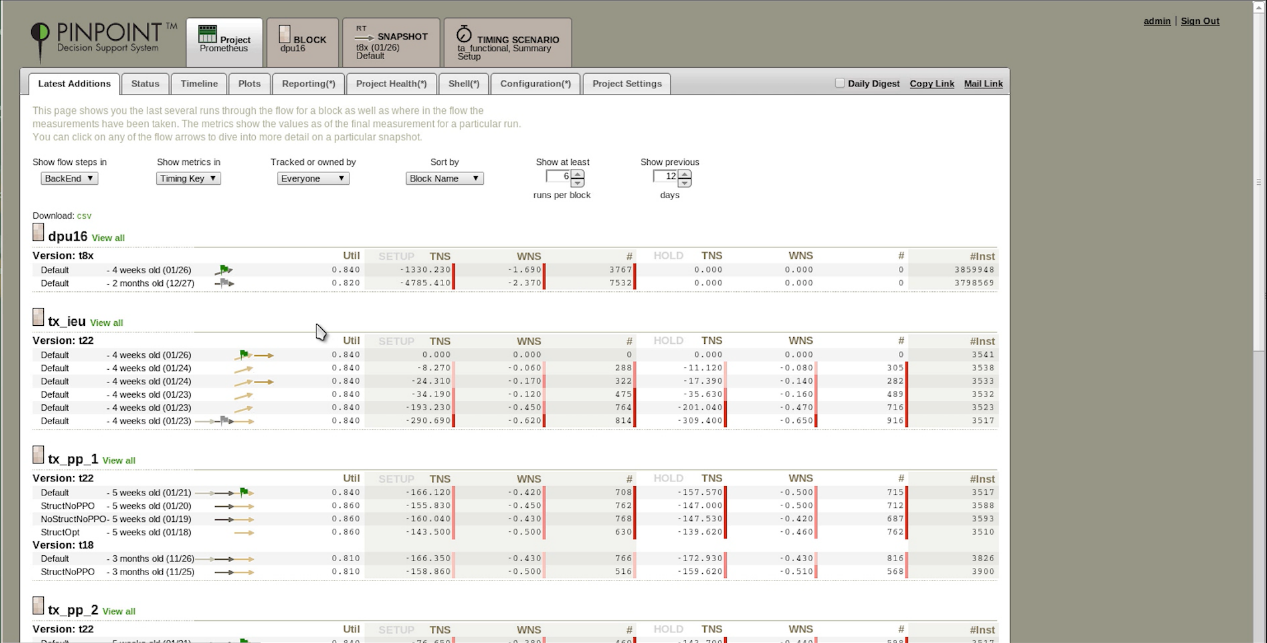

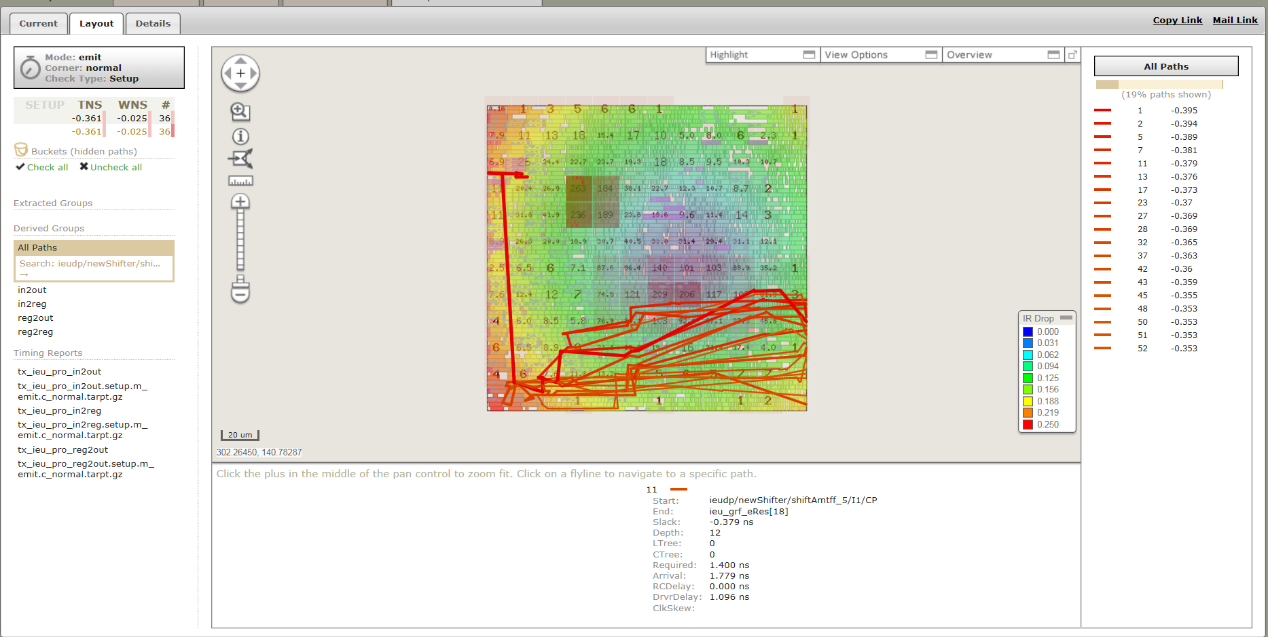

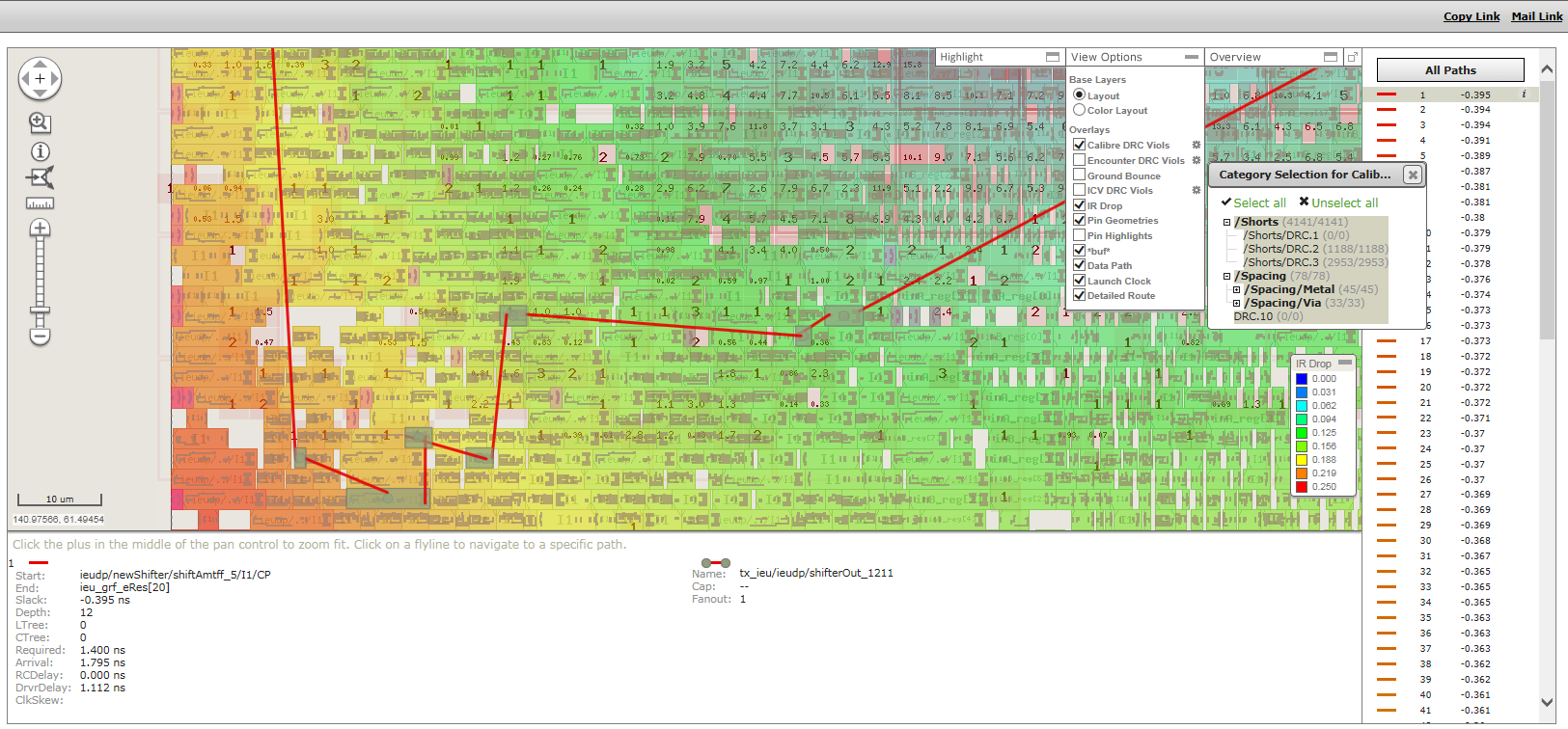

ENOVIA Pinpoint可以自動為設計團隊提煉資料,以各種綜合性視覺化圖表將設計資訊加以分析,在問題變得嚴重之前發現問題。比方說,可將時序路徑(timing path)、接地反壓(ground bounce)、電流電阻壓降(IR Drop) 顯示在佈局上。ENOVIA Pinpoint可客製設計階段,比如說pre-syn、post-syn、DfT等等,將各段資料分別整理與展現。ENOVIA Pinpoint能夠搜集大量多維資料,加以分析,並根據歷史時限把它們顯示在簡單的視覺化儀表板上,從而幫助用戶查看可能偏離正軌的位置。這些趨勢圖有利於說明進程狀態,提升工程人員和管理人員之間的溝通。

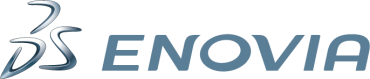

借助ENOVIA Pinpoint,使用者可以獲得重要的設計錯誤排除資訊,從而加快設計進度,達到設計收斂並tape-out的目的。各專案所採集的資料都存儲在各別專案的中央資料庫中。使用者透過流覽器可以以視覺化的方式快速檢視。統一的視覺圖表可綜合顯示來自不同工程問題和專業領域的結果,讓設計團隊之間能夠做更好的溝通和協調,從而加速設計進程。

ENOVIA Pinpoint提供綜合性的調查,快速交叉檢視設計的關鍵資料,找出問題根源

互動式圖形 – 將timing path顯示於佈局上,並提供互動式視窗彈出和向下鑽取功能,便於快速找到根源答案。

可客製試算表 – 選擇和呈現對用戶團隊取得成功的最關鍵資料,迅速發現和調查異常值

縮放和平移 – 平移和縮放佈局,以站在較高層次評估問題。然後放大圖形,從事件層面放大到單元層面,進行故障排除。

【原廠聯結】達梭系統網站 : www.3ds.com

【原廠logo】

【產品logo】

【產品架構圖】

【業務聯絡人】

- 產品經理 楊宜霖

- Tel : (03)5425566分機61245

- Mobile : 0933120585

- e-mail : larry.yang@sti.com.tw